-

Vhdl Binary To Integer Converter Mp4카테고리 없음 2020. 2. 18. 01:02

VHDL Type ConversionPosted by in on 2-10-13Any given VHDL FPGA design may have multiple VHDL types being used. The most common VHDL types used in synthesizable VHDL code are stdlogic, stdlogicvector, signed, unsigned, and integer. Because VHDL is a strongly-typed language, most often differing types cannot be used in the same expression. In cases where you can directly combine two types into one expression, you are really leaving it up to the compiler or synthesis tool to determine how the expression should behave, which is a dangerous thing to do.This article will discuss the following concepts:1. Type casting and conversion functions.2.

The importance of using the appropriate type.3. Common uses and examples.

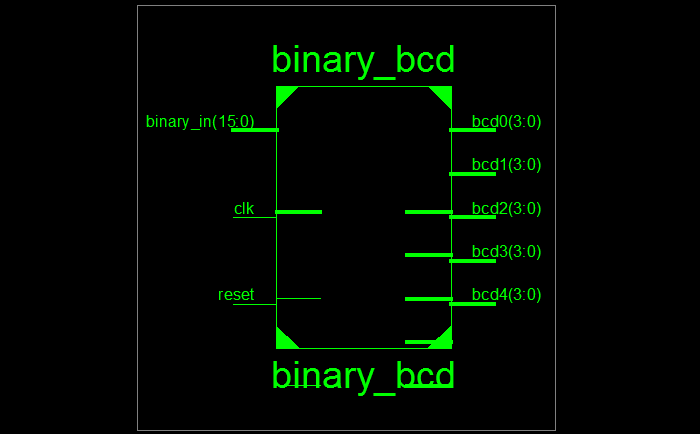

VHDL Type Cast and Conversion FunctionsThe picture below illustrates how to convert between the most common VHDL types.Type casting is used to move between the stdlogicvector type and the signed and unsigned types.cc lang=”vhdl” noborder=”true” tabsize=”4″ lines=”-1″ width=”600″ escaped=”true”–signal definitionssignal slv: stdlogicvector(7 downto 0);signal s: signed(7 downto 0);signal us: unsigned(7 downto 0);–FROM stdlogicvector TO signed/unsignedsgn. Another common use is converting a stdlogicvector or unsigned type to an integer so that it can be used as an array index.

Integer To Binary Converter

Arrays can only be indexed with integers.cc lang=”vhdl” noborder=”true” tabsize=”4″ lines=”-1″ width=”600″ escaped=”true”constant vec: stdlogicvector(15 downto 0);signal count: stdlogicvector(3 downto 0);signal element: stdlogicvector(0 downto 0);element.